반도체 배선 ‘전기 동맥경화’ 뚫어낼 원료물질 개발

- 가

UNIST, 400℃ 고온에도 안정한 루테늄 배선 원료물질 개발

고온 ALD 공정으로 배선 품질·공정 속도 모두 잡아

(왼쪽부터) UNIST 김수현 교수, 히데아키 나카쓰보 연구원(제1저자), 데바난다 모하파트라 교수, 김정하 연구원. UNIST 제공

(왼쪽부터) UNIST 김수현 교수, 히데아키 나카쓰보 연구원(제1저자), 데바난다 모하파트라 교수, 김정하 연구원. UNIST 제공

반도체 회로 선폭이 줄어들면서 발생하는 이른바 ‘전기 동맥경화’ 현상을 해결할 물질이 개발됐다.

울산과학기술원(UNIST) 반도체소재부품대학원 김수현 교수팀은 차세대 반도체 배선 소재인 루테늄의 새로운 원료 물질(전구체)과 이를 적용한 원자층 증착 공정(atomic layer deposition, ALD)을 개발했다고 20일 밝혔다.

금속 배선은 반도체 칩 내부의 수억 개 트랜지스터에 전력을 공급하고 신호를 전달하는 핵심 구조이다.

공정 미세화가 진행되면서 배선 폭이 점점 줄어들고 있는데, 상용 구리 배선은 선폭이 감소할수록 박막의 전기저항이 급격히 증가해 전류가 잘 흐르지 못하고 칩 성능 저하로 이어지는 문제가 있다. 반면 루테늄은 선폭이 줄어들어도 저항 증가가 상대적으로 완만해 차세대 배선 소재로 주목받고 있다. 또한 구리와 달리 별도의 확산방지층이 필요하지 않아 구조를 더욱 간단하게 만들 수 있다는 장점도 있다.

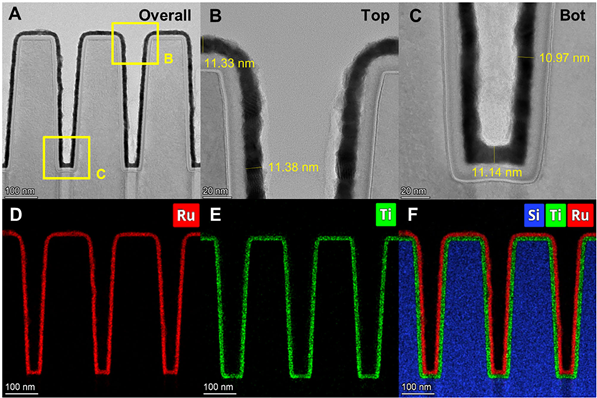

그림. 원료 물질을 사용해 3차원 구조에 균일하게 입혀진 루테늄 박막. (A) 깊고 좁은(고종횡비) 3차원 패턴 구조 전체를 촬영한 TEM 이미지. 루테늄이 질화티타늄(TiN) 표면 위에서 가장 아래 바닥까지 일정한 두께로 코팅돼 있는 모습이 보인다. (B–C) 패턴의 상단과 하단을 각각 확대해 보여준 이미지. 세 위치(상단 11.33nm, 중간 11.38 nm, 하단 10.97~11.14nm)에서 루테늄 두께가 거의 동일해, 구조가 깊어져도 모든 부분에서 균일한 증착이 이루어지는 우수한 단차 피복성을 확인할 수 있다. (D–F) EDS 원소 매핑(각 원소를 색깔별로 구분해 시료 내 원소가 어디에 분포하는지 시각적으로 보여주는 기술)을 통해 TiN 위에 루테늄이 균일하게 덮인 것을 시각적으로 보여준 이미지. 빨간색은 루테늄, 초록색은 티타늄, 파란색은 실리콘이다. UNIST 제공

그림. 원료 물질을 사용해 3차원 구조에 균일하게 입혀진 루테늄 박막. (A) 깊고 좁은(고종횡비) 3차원 패턴 구조 전체를 촬영한 TEM 이미지. 루테늄이 질화티타늄(TiN) 표면 위에서 가장 아래 바닥까지 일정한 두께로 코팅돼 있는 모습이 보인다. (B–C) 패턴의 상단과 하단을 각각 확대해 보여준 이미지. 세 위치(상단 11.33nm, 중간 11.38 nm, 하단 10.97~11.14nm)에서 루테늄 두께가 거의 동일해, 구조가 깊어져도 모든 부분에서 균일한 증착이 이루어지는 우수한 단차 피복성을 확인할 수 있다. (D–F) EDS 원소 매핑(각 원소를 색깔별로 구분해 시료 내 원소가 어디에 분포하는지 시각적으로 보여주는 기술)을 통해 TiN 위에 루테늄이 균일하게 덮인 것을 시각적으로 보여준 이미지. 빨간색은 루테늄, 초록색은 티타늄, 파란색은 실리콘이다. UNIST 제공

연구팀이 개발한 원료 물질은 400℃에서도 분해되지 않아 고품질의 루테늄 배선을 깔 수 있다. 루테늄 배선은 원료 물질을 먼저 기판에 흡착시킨 뒤, 반응 가스를 주입해 원료 물질의 루테늄 금속 부분만 남기고 나머지 부분을 제거하는 ALD 방식으로 이뤄진다. 배선의 품질은 공정 온도가 높아질수록 뛰어나지만, 기존 루테늄 원료 물질은 높은 공정 온도를 견디지 못하고 분해돼 버리는 문제가 있었다.

이 원료 물질로 증착된 루테늄 박막은 열처리 없이도 이상적인 저항률(벌크 7.4μΩ·cm)에 거의 근접한 10.6마이크로옴(μΩ·cm)의 낮은 저항률을 기록했다. 단차 피복성도 95% 이상을 기록했다. 이는 3D 낸드(NAND)와 같이 좁고 깊은 반도체 구조에 박막을 균일하게 입힐 수 있다는 것을 의미한다. 이번 연구에 사용된 원료 물질은 반도체 공정비용과 시간도 줄일 수 있다. 배선이 필요한 곳에만 선택적으로 루테늄이 증착되고, 전기가 통하면 안 되는 절연체 위에는 달라붙지 않는 특성이 있기 때문이다. 절연체 위에 달라붙은 배선은 별도의 식각 공정을 통해 제거해야만 했다. 또 1회 공정에 0.13나노미터(nm, 1.28 Å) 두께의 루테늄 박막을 만들었는데, 이는 기존보다 약 2배 빨라진 속도다.

김수현 교수는 “반도체 소자의 고집적화로 배선 공정의 난이도가 기하급수적으로 높아지는 상황에서, 미세 선폭의 저항 감소와 3D 구조의 증착 균일성, 빠른 증착 속도를 동시에 확보했다는 데 의미가 있다”며 “차세대 로직 및 메모리 반도체 양산 공정의 수율과 성능 경쟁력을 높이는 데 기여할 것”이라고 말했다.

이번 연구는 UNIST와 일본의 귀금속 소재 회사인 다나까 귀금속(TANAKA PRECIOUS METAL TECHNOLOGIES Co., Ltd.)간의 국제 공동 연구를 통해 얻어졌으며, 연구 결과는 저명한 국제 학술지 ‘어드밴스드 사이언스(Advanced Science)’에 11월 23일 온라인 게재됐다. 연구는 산업통상자원부(MOTIE) 기술혁신사업의 지원으로 진행됐다.

송현수 기자 songh@busan.com

당신을 위한 AI 추천 기사

실시간 핫뉴스